고온 챔버 내 온도 모니터링 시스템 개발

Abstract

As semiconductors become smaller, complex and diverse chips must be coupled, requiring next-generation packaging methods that enable high-density integration at low cost. High-density vertical interfaces in 2.5D and 3D packages require tall Cu pillars, which are fabricated using pillar molds created by photolithography. Photolithography requires a photoresist (PR) coating process. Spin PR coating on large rectangular panels increases both spinner size and PR consumption. To address this, inkjet-based PR coatings using PR ink have been proposed. As PR ink is a mixture of PR and solvent, forming the final PR layer requires a baking process after inkjet coating to evaporate the solvent. The panel must be baked at a consistent temperature to produce a PR mold with uniform thickness. This requires a homogeneous temperature rise across the glass panel during baking. Consequently, a temperature-monitoring system was developed to conduct temperature tests at high temperatures instead of using actual processing panels.

Keywords:

Temperature monitoring, High temperature, Chamber, Panel, Heater1. 서 론

반도체가 미세화 되면서 동일 공간 내 복잡하고 다양한 디바이스들을 연결해야 하며 저비용에 디바이스들을 고밀도로 집적할 수 있는 차세대 패키지 기술이 요구되고 있다. 하나의 패키지에 포함된 디바이스의 개수가 늘어날수록 디바이스를 1D 평면에 통합하는 데에는 한계가 있다. 따라서 제한된 공간 내에서 디바이스를 2.5D, 3D로 집적화 하는 칩렛 패키지가 요구되고 있다[1-5].

2.5D, 3D 패키지에서 고밀도 수직 인터페이스를 구성하기 위해서는 Tall Cu pillar가 요구된다. Tall Cu pillar를 제작하기 위해서는 Pillar mold가 필요하다. Pillar mold는 Photolithography 공정을 통해 제작된다. Photolithography 공정은 PR (photoresist)을 코팅한 후 빛을 가해 패턴을 형성하는 공정으로 Etching을 통해 Pillar mold를 제작할 수 있다[6]. Photolithography 공정을 위해서는 PR 코팅 공정이 필요하다. 일반적으로 웨이퍼에 대해서는 Spin 코팅을 통해 PR을 코팅한다. 원형의 Wafer Level Package (WLP)에서 최근에는 수율 향상을 위해 사각의 Panel Level Package (PLP)가 요구되고 있다[7-10]. 사각의 대형 Panel 위에서 Spin 코팅을 진행하기에는 Spinner 사이즈도 커지고 PR 소비량이 증가한다. 이러한 문제를 해결하기 위해 PR 잉크를 이용한 잉크젯 기반의 PR 코팅이 제안되었다. PR을 잉크화하기 위해서는 PR에 Solvent를 조합하게 된다. 최종 PR층을 형성하기 위해서는 잉크젯 코팅 후 Solvent를 증발시키는 Bake 공정이 필요하다. PLP에 대응하여 Bake 공정용 Heater와 챔버가 제작되었다. Bake 공정에서 일정한 두께의 Pillar mold가 형성되려면 Panel에서 균일한 일정 온도가 유지되어야 한다[11,12]. 이를 위해서는 Bake 공정 내에서 Glass panel이 균일하게 온도가 상승되었는지 확인이 필요하다. 기존에는 기판 주변의 Holder나 Heater 온도를 모니터링하여 조건을 확보하는 연구들이 확인되었다[13,14]. 이는 직접적으로 기판의 온도를 측정한 것이 아니기 때문에 온도 정확도의 문제가 있었다.

본 연구에서는 고온에서 실제 공정용 Panel을 대신하여 온도 테스트를 할 수 있는 온도 모니터링 시스템을 개발했다. Bake용 챔버를 고려하여 고온에 적합한 PCB 기판을 설계하고 온도 데이터 신호처리 및 모니터링할 수 있도록 회로 설계를 진행했다. 실제로 모니터링 시스템을 제작하고 Bake 챔버에 적용하여 챔버 내부에서 공정 단의 온도 모니터링을 통해 온도 균일도를 확인하였다.

2. Bake 공정 챔버

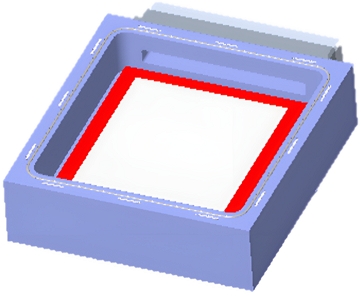

본 연구에서 목표로 하는 Glass panel은 일반적으로 PLP에 사용하는 크기로 650 × 650 mm2이다[15]. Bake 공정이 진행되는 챔버의 Heater는 Glass panel이 균일하게 온도 상승이 가능하도록 충분히 커야 한다. 본 연구에서 활용하는 Heater의 크기는 800 × 800 mm2 이며 6개의 구간으로 나누어져 있다. Fig. 1은 Heater와 Glass panel을 나타낸다.

온도 모니터링이 시스템이 적용될 챔버는 Fig. 2와 같고 크기는 1050 × 1050 × 240 mm2 이다. 챔버 내부에 Heater가 있고 Glass panel은 Heater위에 있다. Bake 공정 시에는 챔버가 밀폐되며 Heater에 의해 Glass panel 온도가 상승한다. 챔버가 밀폐되기 때문에 공정 시에는 Glass panel의 온도 측정이 어렵다. Bake 공정의 결과물은 온도 균일도에 따라서 PR 코팅 균일도가 달라진다. 따라서 공정이 일어나는 Glass panel 쪽의 온도 균일도를 모니터링해야 PR 코팅 균일도를 확보할 수 있다. 본 연구에서는 Glass panel와 유사한 크기의 온도 모니터링 시스템을 개발하여 공정 시 Heater에 의해 가열된 Glass panel의 온도를 측정하고자 한다.

3. 온도 모니터링 시스템

3.1 개념 설계

앞에서 설명했듯이 온도 모니터링 시스템은 챔버 내에 위치하여 고온의 환경에 견딜 수 있어야 한다. 고온을 측정할 수 있는 온도 센서로 본 연구에서는 Texas Instruments사의 TMP126 IC를 적용하였다. TMP126 IC는 175oC까지 측정이 가능하고, 범위에 따라서는 최소 ±0.25oC 및 최대 ±0.75oC의 정확도를 갖는다.

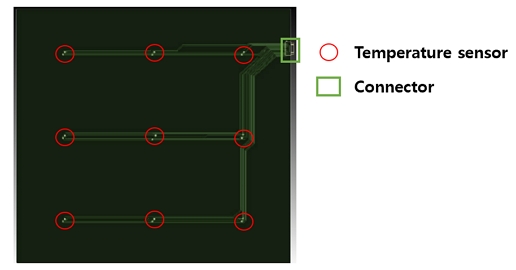

대면적의 온도를 측정하기 위해서는 다수의 온도 센서가 필요하며 9개의 구역으로 나누어 구역 별로 측정할 수 있게 구성했다. 9개의 TMP126 IC는 3개의 그룹으로 나누어서 온도 데이터를 취득하도록 설계하였다. ATmega328P를 SPI 마스터로 선택하고 TMP126 3개 연결하여 그룹별로 온도 데이터를 취득한다.

각 센서 데이터를 챔버 외부의 PC로 전송하기 위한 인터페이스 설계도 필요하다. 온도 센서 TMP126 IC를 기준으로 외부 MCU와 SPI 통신을 통해서 측정한 온도 값을 전달하는 인터페이스 회로를 설계하였다. TMP126 IC는 측정된 온도 값을 SPI 통신 기반으로 전달하는데 Chip Select 핀, Serial I/O 핀, SCLK의 클럭 핀으로 제어가 가능하다.

챔버 내부에 위치할 PCB의 인터페이스 커넥터는 고온에서 견딜 수 있는 MDM-31PCBR를 채택하여 설계하였다. MDM-PCB 커넥터는 PCB에 삽입되는 Angled 타입의 커넥터이고 MDM-F222는 케이블이 연결되어 챔버의 인터페이스용 멀티핀 커넥터에 연결되는 구조로 설계하였다.

인터페이스 PCB는 고온 PCB와 PC 사이에 연결되어 측정된 온도 값을 순차적으로 PC에 전달해주는 기능을 한다. MCU는 ATmega2560을 적용하였고 이더넷을 통해서 PC와 통신을 수행한다.

챔버 외부의 인터페이스 PCB와 장거리 연결을 고려한 PCB 개발을 위한 회로 설계도 진행하였다. 설계 결과는 Fig. 3과 같다. 9개의 센서들이 회로로 인터페이스와 연결되어 외부로 데이터를 보낼 수 있는 구조이다.

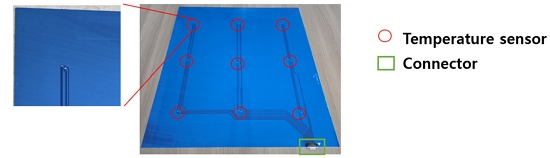

설계 후 제작한 온도 모니터링 시스템은 Fig. 4와 같다. 내열성의 고온용 PCB로 제작하였고 9개의 온도센서가 균일하게 배치되어 있다. 온도 모니터링 시스템의 온도 센서는 PCB에서 Heater를 향하는 면에 위치하도록 배치했다.

회로의 끝에는 온도 데이터가 모여서 Feedthrough 쪽으로 빠져나갈 수 있도록 커넥터가 제작되었다.

4. 온도 모니터링 실험

4.1 실험 구성

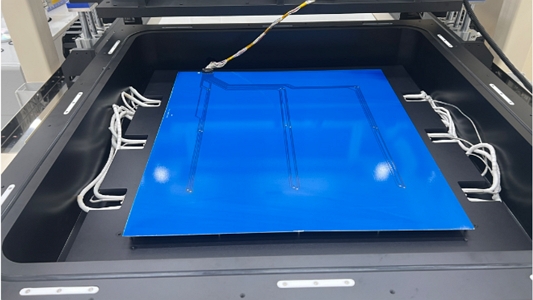

본 연구에서 개발한 모니터링 시스템을 검증하기 위해 Fig. 5와 같이 테스트베드를 구성하였다. Bake 챔버의 Heater 위에 온도 모니터링 시스템을 위치하였다. 케이블은 Feedthrough를 통해 외부로 빠져나와 PC로 연결하여 데이터를 취득하였다.

4.2. 실험 결과

실험에서는 실제 공정과 유사한 환경을 구성하기 위하여 Bake 챔버의 상부 Cover를 닫고 Heater를 통해 열을 가했고 챔버 내부의 온도 모니터링 시스템으로 온도 균일도를 측정하였다. 본 연구에서 활용하는 Heater는 6개 구역으로 나누어져 있어 온도 상승 시에는 구역별로 제어가 된다. 따라서 온도 상승 시보다는 공정 온도에 도달한 후 Glass panel에서 온도 균일도가 중요하다. PR의 Soft bake 공정 온도가 120oC이다. 온도 균일도의 정의는 식 (1)과 같다.

| (1) |

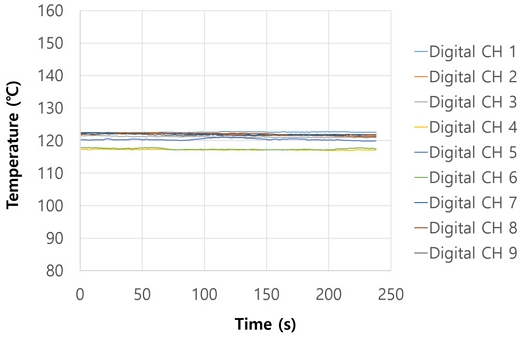

본 실험에서는 개발한 모니터링 시스템에서 120oC를 유지하면서 9개 센서에 대한 데이터를 취득하고 온도 균일도를 계산하였다.

온도 모니터링 시스템의 120oC에서 온도 분포는 Fig 6과 같다. 온도가 120oC로 유지되는 238초 동안 9개 센서에서 온도를 측정했다.

실험에 대한 온도 균일도 결과는 Table 1에 정리하였다. 120oC 온도를 기준으로 9개 센서에서 측정된 온도 최대값은 122.8oC, 최소값은 117oC로 ±3oC의 온도 균일도가 계산되었다.

본 실험 결과 공정이 일어나는 Panel 단에서 온도를 측정할 수 있는 모니터링 시스템을 통해 공정 조건을 확보할 수 있음을 확인하였다.

기존에는 기판 주변의 온도를 측정하여 공정 조건을 확보하였으나 본 연구에서 개발한 모니터링 시스템을 통해 내부 환경을 확인하기 어려운 고온의 환경에서도 실시간 온도 모니터링이 가능함을 확인하였다.

5. 결 론

본 연구에서는 Bake 챔버 내에서 공정 및 환경 온도를 모니터링할 수 있는 측정 시스템을 개발하였다. 실제 공정이 일어나는 패널 사이즈와 유사하게 크기를 선정하였고 9개의 센서를 배치하여 패널 영역의 온도를 측정할 수 있도록 개념 설계를 진행했다.

Bake 챔버 내에서 온도를 측정할 수 있도록 고온에 적합한 온도 센서 IC를 선정하였다. 온도 센서 데이터를 PC까지 전송할 수 있도록 IC를 기준으로 인터페이스 회로를 설계하였다. 인터페이스 커넥터 역시 고온에 적합하게 선정하였고 9개 센서는 3개의 그룹으로 나누어서 온도 데이터를 취득하도록 설계하였다. 온도 모니터링 시스템의 케이블은 Bake 챔버 내부와 외부를 연결하는 Feedthrough를 통해 PC로 연결되도록 설계하였다.

설계된 온도 모니터링 시스템은 PCB로 공정 패널과 유사하게 제작하였고 취득한 온도 데이터를 시각화할 수 있게 UI를 구성하였다.

제작된 온도 모니터링 시스템은 테스트베드를 구성하여 성능을 검증하였다. Bake 챔버 내에 온도 모니터링 시스템을 위치시키고 실제 공정과 유사하게 밀폐된 챔버 내부 Heater를 통해 열을 인가하였다. 온도 모니터링 시스템을 통해 공정 온도인 120oC에서 Panel 전반의 온도 균일도를 확인하였다.

PR의 Soft bake 공정 조건인 120oC를 유지하기 위해 Heater를 조절하였고 온도 모니터링 시스템을 통해 120oC±3oC의 온도균일도를 확인하였다.

본 연구를 통해 개발된 모니터링 시스템은 내부 환경을 확인하기 어려운 고온의 환경에서 실시간 온도 모니터링이 가능함을 확인했다. Bake 공정 외에도 밀폐된 환경에서 공정 조건을 확보하기 위한 테스트 시스템으로 본 연구에서 개발한 모니터링 시스템을 다양하게 적용할 수 있을 것으로 기대된다.

Acknowledgments

이 연구는 2025년 산업통상자원부의 ‘FOWLP/PLP를 위한 대형기판용 Plasma 전처리 기반 PR Coating 장비 개발’ 사업의 지원을 받아 수행되었음(No. 20023103, PKM25110).

References

-

Sharma, D. D., Pasdast, G., Tiagaraj, S., Aygün, K., 2024, High-Performance, Power-Efficient Three-Dimensional System-in-Package Designs With Universal Chiplet Interconnect Express, Nat. Electron., 7 244-254.

[https://doi.org/10.1038/s41928-024-01126-y]

-

Chen, Z., Zhang, J., Wang, S., Wong, C.-P, 2024, Challenges and Prospects for Advanced Packaging, Fundam. Res., 4:6 1455-1458.

[https://doi.org/10.1016/j.fmre.2023.04.014]

-

Das, A., Palesi, M., Kim, J., Pande, P. P., 2024, Chip and Package-Scale Interconnects for General-Purpose, Domain-Specific, and Quantum Computing Systems—Overview, Challenges, and Opportunities, IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 14:3 354-370.

[https://doi.org/10.1109/JETCAS.2024.3445829]

-

Fukushima, T., Alm, A., Hanna, A., Jangam, S. C., Bajwa, A. A., lyer S. S., 2018, Flexible Hybrid Electronics Technology Using Die-First FOWLP for High-Performance and Scalable Heterogeneous System Integration, IEEE Transactions on Components, Packaging and Manufacturing Technology, 8:10 1738-1746.

[https://doi.org/10.1109/TCPMT.2018.2871603]

-

Lau, J. H., 2022, Recent Advances and Trends in Advanced Packaging, IEEE Transactions on Components, Packaging and Manufacturing Technology, 12:2 228-252.

[https://doi.org/10.1109/TCPMT.2022.3144461]

- Baek, S.-Y., 2018, A study on processing characteristics of plasma etching using photo lithography, Design & Manufacturing, 12:1 47-51, <https://koreascience.kr/article/JAKO201836256831208.page, >.

-

Che, F. X., Yamamoto, K., Rao, V. S., Sekhar, V. N., 2019, Panel Warpage of Fan-Out Panel-Level Packaging Using RDL-First Technology, IEEE Transactions on Components, Packaging and Manufacturing Technology, 10:2 304-313.

[https://doi.org/10.1109/TCPMT.2019.2929529]

-

Shinoda, K. -I, Shelton, D., Suda, H., Goto, Y., Urushihara, K., Mori, K., 2021, Study of Submicron Panel-Level Packaging in Mass-Production, IEEE 71st Electronic Components and Technology Conference (ECTC), 2105-2110.

[https://doi.org/10.1109/ECTC32696.2021.00331]

-

Lin, Y. -M., Wu, S.-T., Wang, C.-M., Lee, C.-H., Huang, S.-Y., Lin, A.-Y., 2019, An RDL-First Fan-Out Panel-Level Package for Heterogeneous Integration Applications, IEEE 69th Electronic Components and Technology Conference (ECTC).

[https://doi.org/10.1109/ECTC.2019.00225]

-

H. Seol, Y. Choi, J. Park, S. Kim, 2019, Warpage Analysis of a Panel Level Packaging, J. Korean Soc. Manuf. Technol. Eng., 28:4 203-209.

[https://doi.org/10.7735/ksmte.2019.28.4.203]

-

Fujiwara, T., Kinoshita, H., Ohue, H., Fujii, T., 2020, Methodology for the Formation of Photoresist Films With Uniform Thicknesses of Several Hundred Micrometers, SN Appl. Sci., 2 1907.

[https://doi.org/10.1007/s42452-020-03741-8]

-

Yang, Y. -K., Chang, T.-C., 2006, Experimental Analysis and Optimization of a Photo Resist Coating Process for Photolithography in Wafer Fabrication, Microelectronics Journal, 37:8 746-751.

[https://doi.org/10.1016/j.mejo.2005.10.006]

-

Mori, S., Fukuya, M., Suzuki, M., 2007, Synthesis of Carbon Nanofibers Using Carbon Monoxide DC Plasma at Room Temperature, Transactions of the Materials Research Society of Japan, 32:2 513-516.

[https://doi.org/10.14723/tmrsj.32.513]

-

Musil, J., Heřman, D. Šícha, J., 2006, Low-temperature Sputtering of Crystalline Ti O2 Films, J. Vac. Sci. Technol. A, 24 521-528.

[https://doi.org/10.1116/1.2187993]

-

O’Toole, E., Silva, J. L., Cardoso, F., Silva, J., Alves, L., Souto, M., 2022, A Hybrid Panel Level Package (Hybrid PLP) Technology Based on a 650-mm x 650-mm Platform, IEEE 72nd Electronic Components and Technology Conference (ECTC), 824-827.

[https://doi.org/10.1109/ECTC51906.2022.00135]

Senior Researcher at the Korea Institute of Industrial Technology (KITECH). His research interests include Precision Engineering, Piezo-flexure Stages, and Semiconductor Equipment.

E-mail: jh8145@kitech.re.kr